对于许多进行PCB布局设计的人来说,射频走线因涉及到模拟信号、EMC(电磁兼容性)、阻抗匹配等问题,通常在设计时会参考芯片手册中提供的建议。例如,当射频走线需要进行兼容设计时,通常会采用两个封装重叠共享的方式来处理,目的是防止因射频信号阻抗不连续而导致信号在边角处辐射。

本文利用实际案例来分享射频模块在PCB设计中应该如何处理co-layout(共布局)问题。

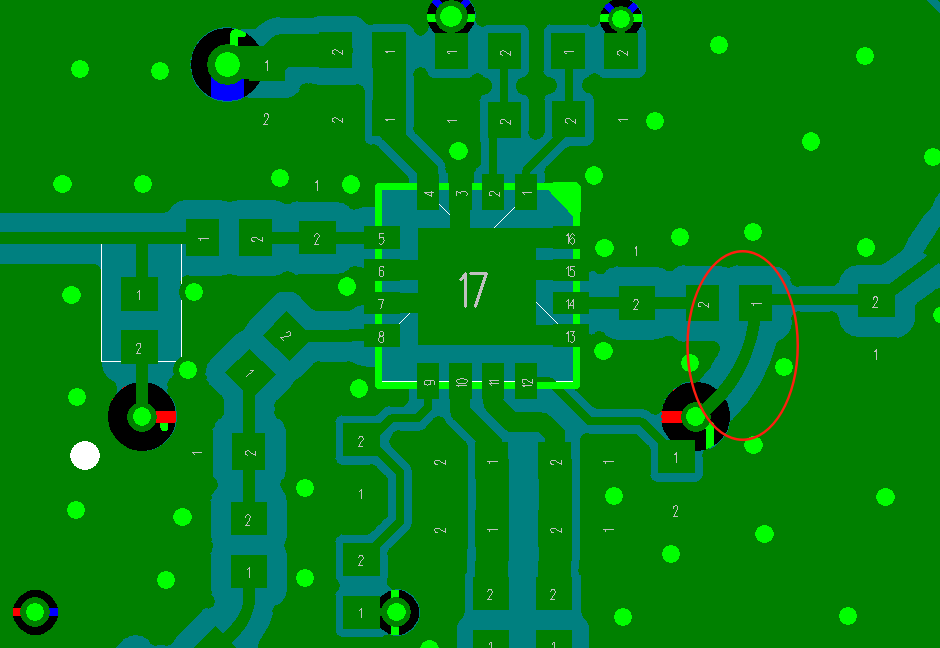

如下图所示是A客户产品中FEM射频模块的布局设计,FEM模块两端都设计了一个分线的位置,主要作用是进行兼容设计,但关键问题是元件并未真正做到co-layout,只是通过射频线调整其方向。这样的处理方式相当于在RF路径上多出一段导线,导致整段的特性阻抗失配,从而产生EMI问题。

如下图所示,我们通过网络分析仪测量到目前的特性阻抗情况已经处于失配状态,通过元件匹配调整已无法得到有效改善。

针对这种情况的调整策略就是在共布局中多增加一个0欧姆电阻。在射频电路中常采用共布局方式,通过共享封装(Footprint)来实现路径重叠,避免因阻抗不匹配而导致的EMI干扰。如下面的图所示,通过两个同封装的元件重叠焊盘的方式,不仅可以减少90度转折的残段,还能确保阻抗的连续性。

1.什么是射频Co-layout?

射频Co-layout是指在设计和制造过程中,将多个射频元件或系统元件在物理空间中合理安排,以确保它们之间的互连最小化,同时最大化信号传输的效率和可靠性。

2.为什么射频Co-layout很重要?

射频Co-layout可以减少信号干扰、提高系统性能、降低功耗、优化空间利用率,并减少制造成本。

3.射频Co-layout的主要挑战有哪些?

挑战包括元件间的电磁干扰(EMI)、热效应管理、信号完整性以及互连的复杂性等。

4.如何评估射频Co-layout的效果?

可以通过信号完整性分析、电磁兼容性测试(EMC)以及实际性能测试来进行评估。

5. 射频Co-layout对系统功耗有何影响?

合理的布局可以减少不必要的信号传输损耗,从而降低系统功耗。